ASIC Basics

Last Updated: [last-modified] (UTC)

The Nexus ASIC

The ASIC is the powerhouse of the Nexus switch. The ASIC, or Application Specific Integrated Circuit, is a special purpose sillicon chip. The ASIC achieves high forwarding speeds as packets pass through the forwarding plane.

An ASIC in a general sense is not unique to networking. Many electronic devices use them for some specific purpose. In contrast, general processors, such as the CPU, perform many different tasks.

Nexus ASIC

This article generally uses the Nexus 5000 and 5500 series for reference

Different routers and switches will use ASICs in different ways. Even within the Nexus family, different ASICs achieve different goals. The Nexus 5000 series, for example, uses two different ASIC’s.

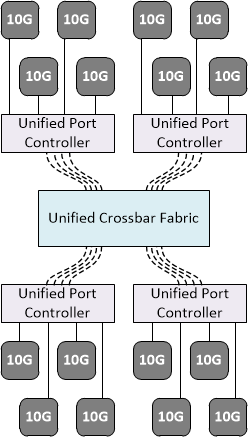

The Unified Port Controller (UPC) is the first N5K ASIC. Each UPC chip controls a small group of 4 or 8 ports, depending on whether the Nexus is a 5000 series or 5500 series. It handles processing packets upon ingress or egress for the port it manages. It also handles forwarding decisions between ports.

The second ASIC type is the Unified Crossbar Fabric (UCF). This is a bridge between many UPC’s, and manages packet switching and scheduling. This couples a UPC for the ingress port to a UPC for the egress port.

The second ASIC type is the Unified Crossbar Fabric (UCF). This is a bridge between many UPC’s, and manages packet switching and scheduling. This couples a UPC for the ingress port to a UPC for the egress port.

The Nexus switches use ASICs in cut-through switching mode. This achieves low latency and line-rate speeds. The 5548 has a latency of 2 microseconds. The Nexus switches transparently forward packets through the ASICs. This achieves high-performance in the data-plane.

The ASICs have a special place in forwarding packets. This means that querying them for packet drops is beneficial during troubleshooting.

ASIC Separation

It is good practice to spread etherchannel or LAG ports across different ASIC chips. For example, a four-port etherchannel may use two ports connected to UPC #1, and two on UPC #2.

This is to protect against ASIC failure. In the rare occasions when a port fails, there’s a good chance that it’s actually the ASIC that has failed. This may mean that a group of ports has or soon will fail. If all ports in an etherchannel are on a single failed ASIC, then the etherchannel will also fail.

Another reason to spread links across ASIC’s is because of oversubscription. Four 10G ports may have a theoretical capacity of 40G throughput. However, the ASIC that manages them may only have a throughput of 30G or 35G. This type of oversubscription works on the theory that not all ports will reach full capacity at once.

There’s good news for N5K owners though, as each 10G port is mapped at 12G to the ASIC. This means that the N5K is undersubscribed. This is to get line rate (one of the reasons for the high Nexus price tag). If you’re expecting ports to reach capacity, understand the internal architecture of your switch.

The show hardware internal carmel command lists the ASICs in a Nexus 5500. Different switches have different ASIC names, so the commands vary between models. For example, the Nexus 5000 series ASIC is ‘Gatos’ and the Nexus 5500 series is ‘Carmel‘.

N5500# show hardware internal carmel Carmel ASIC Info: idx|glb|sl|as|pts|state |kaddr |uaddr |bus:fn|irq(hex)| MMmode[0:7] |diag ---+---+--+--+---+------+--------+--------+------+--------+---------------+---- 0 |0 |0 |0 |8 |ff |fa800000|676cd000|f:0 |d2 |x:x:x:x:x:x:x:x|pass 1 |1 |0 |1 |8 |ff |fa000000|66ecd000|11:0 |d1 |x:g:x:x:x:g:x:g|pass 2 |2 |0 |2 |8 |ff |f9800000|666cd000|13:0 |d0 |x:x:x:x:x:x:x:x|pass 3 |3 |0 |3 |8 |ff |f8000000|65ecd000|19:0 |cf |g:x:g:g:g:g:g:g|pass 4 |4 |0 |4 |2 |ff |f7800000|656cd000|1b:0 |ce |-:-:-:-:s:s:-:-|pass 5 |8 |2 |0 |8 |ff |f3000000|64ca4000|9:0 |cc |x:x:x:x:x:x:x:x|pass 6 |9 |2 |1 |8 |ff |f4000000|644a4000|8:0 |cb |x:x:x:x:x:x:x:x|pass

The show hardware internal carmel all-ports command shows which port maps to each ASIC. This is useful when designing ASIC separation.

The name column is the internal port name, and the car column is the Carmel Number (the ASIC) that the port maps to. Mac is the port number in the ASIC.

N5500# show hardware internal carmel all-ports Carmel Port Info: name |log|car|mac|flag|adm|opr|m:s:l|ipt|fab|xcar|xpt|if_index|diag|ucVer -------+---+---+---+----+---+---+-----+---+---+----+---+--------+----+----- xgb1/2 |1 |0 |0 -|b7 |en |up |0:0:f|0 |92 |0 |0 |1a001000|pass| 4.0b xgb1/1 |0 |0 |1 -|b7 |en |up |1:1:f|1 |88 |0 |0 |1a000000|pass| 4.0b xgb1/4 |3 |0 |2 -|b7 |en |up |2:2:f|2 |93 |0 |0 |1a003000|pass| 4.0b xgb1/3 |2 |0 |3 -|b7 |en |up |3:3:f|3 |89 |0 |0 |1a002000|pass| 4.0b xgb1/6 |5 |0 |4 -|b7 |en |up |4:4:f|4 |90 |0 |0 |1a005000|pass| 4.0b xgb1/5 |4 |0 |5 -|b7 |en |up |5:5:f|5 |94 |0 |0 |1a004000|pass| 4.0b xgb1/8 |7 |0 |6 -|b7 |en |up |6:6:f|6 |95 |0 |0 |1a007000|pass| 4.0b xgb1/7 |6 |0 |7 -|b7 |en |up |7:7:f|7 |91 |0 |0 |1a006000|pass| 4.0b xgb1/10|9 |1 |0 -|b7 |dis|dn |0:0:f|0 |80 |0 |0 |1a009000|pass| 4.0b 1gb1/9 |8 |1 |1 -|b7 |en |up |1:1:0|1 |87 |0 |0 |1a008000|pass| 4.0b xgb1/12|11 |1 |2 -|b7 |en |up |2:2:f|2 |81 |0 |0 |1a00b000|pass| 4.0b xgb1/11|10 |1 |3 -|b7 |en |up |3:3:f|3 |86 |0 |0 |1a00a000|pass| 4.0b xgb1/14|13 |1 |4 -|b7 |dis|dn |4:4:f|4 |82 |0 |0 |1a00d000|pass| 4.0b 1gb1/13|12 |1 |5 -|b7 |en |up |5:5:0|5 |85 |0 |0 |1a00c000|pass| 4.0b xgb1/16|15 |1 |6 -|b7 |dis|dn |6:6:f|6 |83 |0 |0 |1a00f000|pass| 4.0b 1gb1/15|14 |1 |7 -|b7 |en |dn |7:7:0|7 |84 |0 |0 |1a00e000|pass| 4.0b xgb1/18|17 |2 |0 -|b7 |en |up |0:0:f|0 |75 |0 |0 |1a011000|pass| 4.0b xgb1/17|16 |2 |1 -|b7 |en |up |1:1:f|1 |76 |0 |0 |1a010000|pass| 4.0b xgb1/20|19 |2 |2 -|b7 |en |up |2:2:f|2 |74 |0 |0 |1a013000|pass| 4.0b xgb1/19|18 |2 |3 -|b7 |en |up |3:3:f|3 |77 |0 |0 |1a012000|pass| 4.0b xgb1/22|21 |2 |4 -|b7 |dis|dn |4:4:f|4 |78 |0 |0 |1a015000|pass| 4.0b xgb1/21|20 |2 |5 -|b7 |dis|dn |5:5:f|5 |73 |0 |0 |1a014000|pass| 4.0b xgb1/24|23 |2 |6 -|b7 |dis|dn |6:6:f|6 |72 |0 |0 |1a017000|pass| 4.0b xgb1/23|22 |2 |7 -|b7 |dis|dn |7:7:f|7 |79 |0 |0 |1a016000|pass| 4.0b 1gb1/25|24 |3 |0 -|b7 |en |dn |0:0:0|0 |71 |0 |0 |1a018000|pass| 4.0b xgb1/26|25 |3 |1 -|b7 |dis|dn |1:1:f|1 |64 |0 |0 |1a019000|pass| 4.0b 1gb1/27|26 |3 |2 -|b7 |en |up |2:2:0|2 |65 |0 |0 |1a01a000|pass| 4.0b 1gb1/28|27 |3 |3 -|b7 |en |up |3:3:0|3 |70 |0 |0 |1a01b000|pass| 4.0b 1gb1/29|28 |3 |4 -|b7 |en |up |4:4:0|4 |66 |0 |0 |1a01c000|pass| 4.0b 1gb1/30|29 |3 |5 -|b7 |en |up |5:5:0|5 |69 |0 |0 |1a01d000|pass| 4.0b 1gb1/31|30 |3 |6 -|b7 |en |up |6:6:0|6 |67 |0 |0 |1a01e000|pass| 4.0b 1gb1/32|31 |3 |7 -|b7 |en |up |7:7:0|7 |68 |0 |0 |1a01f000|pass| 4.0b sup0 |32 |4 |4 -|b7 |en |dn |4:4:0|4 |62 |0 |0 |15020000|pass| 0.00 sup1 |33 |4 |5 -|b7 |en |dn |5:5:1|5 |59 |0 |0 |15010000|pass| 0.00 xgb3/1 |0 |0 |0 p|b7 |en |up |0:0:f|0 |37 |0 |0 |1a100000|pass| 0.00 xgb3/2 |1 |0 |1 p|b7 |en |up |1:1:f|1 |44 |0 |0 |1a101000|pass| 0.00 xgb3/3 |2 |0 |2 p|b7 |en |up |2:2:f|2 |36 |0 |0 |1a102000|pass| 0.00 xgb3/4 |3 |0 |3 p|b7 |en |up |3:3:f|3 |43 |0 |0 |1a103000|pass| 0.00 xgb3/5 |4 |0 |4 p|b7 |en |up |4:4:f|4 |39 |0 |0 |1a104000|pass| 0.00 xgb3/6 |5 |0 |5 p|b7 |en |up |5:5:f|5 |32 |0 |0 |1a105000|pass| 0.00 xgb3/7 |6 |0 |6 p|b7 |en |up |6:6:f|6 |33 |0 |0 |1a106000|pass| 0.00 xgb3/8 |7 |0 |7 p|b7 |en |up |7:7:f|7 |42 |0 |0 |1a107000|pass| 0.00 xgb3/9 |8 |1 |0 p|b7 |en |up |0:0:f|0 |34 |0 |0 |1a108000|pass| 0.00 xgb3/10|9 |1 |1 p|b7 |en |up |1:1:f|1 |41 |0 |0 |1a109000|pass| 0.00 xgb3/11|10 |1 |2 p|b7 |en |up |2:2:f|2 |40 |0 |0 |1a10a000|pass| 0.00 xgb3/12|11 |1 |3 p|b7 |en |up |3:3:f|3 |35 |0 |0 |1a10b000|pass| 0.00 xgb3/13|12 |1 |4 p|b7 |en |up |4:4:f|4 |20 |0 |0 |1a10c000|pass| 0.00 xgb3/14|13 |1 |5 p|b7 |en |up |5:5:f|5 |31 |0 |0 |1a10d000|pass| 0.00 xgb3/15|14 |1 |6 p|b7 |en |up |6:6:f|6 |21 |0 |0 |1a10e000|pass| 0.00 xgb3/16|15 |1 |7 p|b7 |en |up |7:7:f|7 |30 |0 |0 |1a10f000|pass| 0.00 Done.

Is Separation Necessary?

Is it really necessary to go to all the effort of separating ASICs? It depends on where you are in the design lifecycle, and the level of risk you are willing to accept.

If you’re still in the design phase, it may be worth spending time thinking about ASIC separation. It won’t take a lot longer, as it’s just a matter of selecting appropriate ports for the etherchannel. If your switches are already in production, then it may not be worth going back and changing the design.

It’s a rare occurance to lose an ASIC, so the risk is quite low. If you’re in an industry with no room for error, it may be worth your time to consider ASIC separation. This eliminates another potential failure point.

Another way to mitigate this risk is to use virtual port-channels. vPC’s spread links across two different switches, and thus different ASICs. Keep in mind that the peer-link and keep-alive would still need ASIC separation.

The important factor is to consider your circumstances. You may have a switch such as the Nexus 93180 which only has one ASIC. This does not support ASIC separation. See the Cisco Live link below for more on this point.

Further Reading

Packet Pushers – Cisco Nexus 5500: Front Panel Port To Internal ASIC Layout From BRKARC-3452

Cisco Live – BRKARC-2222 – Cisco Nexus 9000 Architecture